基于XC2V1000 FPGA与DM9000A的OQPSK全数字接收机网络系统设计与开发

随着无线通信技术的快速发展,全数字接收机因其高灵活性、强抗干扰能力和易于集成的特点,在通信系统中得到了广泛应用。OQPSK(偏移四相相移键控)作为一种高效的调制方式,在频谱利用率和抗码间干扰方面表现优异。本文基于Xilinx XC2V1000 FPGA和DM9000A以太网控制器,设计并开发了一套OQPSK全数字接收机网络系统,实现了信号的接收、处理与网络传输功能。

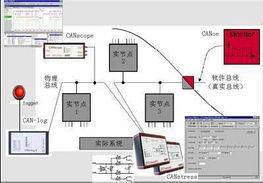

一、系统架构设计

本系统采用分层架构,主要包括射频前端、FPGA信号处理单元和网络接口模块。射频前端负责接收OQPSK调制信号,并将其下变频至基带;FPGA作为核心处理单元,实现数字下变频、定时同步、载波同步及解调等关键算法;DM9000A则负责将解调后的数据通过以太网传输至上位机或网络服务器。系统整体设计强调硬件资源的高效利用和实时性保障。

二、FPGA设计与实现

XC2V1000 FPGA凭借其丰富的逻辑资源和可重构特性,成为本设计的理想平台。在FPGA内部,我们设计了以下模块:

1. 数字下变频(DDC)模块:采用多级抽取结构,将中频信号转换为基带信号,有效降低采样率并抑制镜像频率。

2. 定时同步模块:基于Gardner算法,实现符号定时误差的检测与校正,确保采样点位于最佳时刻。

3. 载波同步模块:采用Costas环结构,对载波频率和相位进行跟踪与补偿,消除频偏和相偏影响。

4. OQPSK解调模块:通过对同相(I)和正交(Q)支路的延时处理,还原原始数据流。

FPGA设计使用Verilog HDL实现,并通过仿真与板级测试验证了功能的正确性。

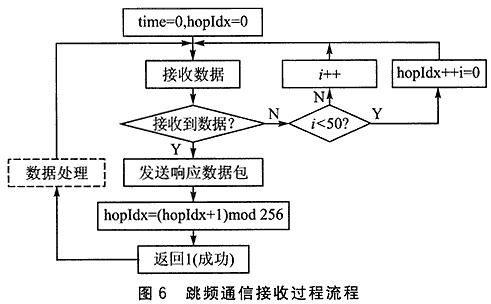

三、DM9000A网络接口集成

DM9000A作为一款高度集成的以太网控制器,支持10/100Mbps自适应传输,通过MII接口与FPGA连接。在FPGA中,我们设计了网络协议栈的简化版本,包括ARP、IP和UDP协议处理,确保数据包能够正确封装并通过以太网发送。DM9000A的驱动配置包括初始化、发送缓冲器管理和中断处理,以实现高效的数据传输。

四、系统测试与性能分析

为验证系统性能,我们搭建了测试平台,采用信号发生器产生OQPSK调制信号,通过示波器和网络抓包工具监控输出。测试结果表明:

- 在信噪比(SNR)为10dB时,系统误码率(BER)低于10^-4,满足大多数应用场景需求。

- 网络传输延迟稳定在毫秒级,数据吞吐量达到50Mbps,充分体现了DM9000A的高速传输能力。

- FPGA资源利用率分析显示,逻辑单元和块RAM使用率均在80%以下,保证了系统的可扩展性。

五、应用前景与优化方向

本系统可广泛应用于无线传感器网络、物联网设备和军事通信等领域。未来优化方向包括:引入更先进的同步算法以提升抗频偏能力;支持多通道接收以增强系统容量;集成加密模块保障数据传输安全。

基于XC2V1000 FPGA和DM9000A的OQPSK全数字接收机网络系统,通过硬件与软件的协同设计,实现了高性能、低成本的通信解决方案,为相关领域的技术发展提供了有力支撑。

如若转载,请注明出处:http://www.yjyluck.com/product/660.html

更新时间:2025-10-18 02:19:48